V 1.21 04/05/21

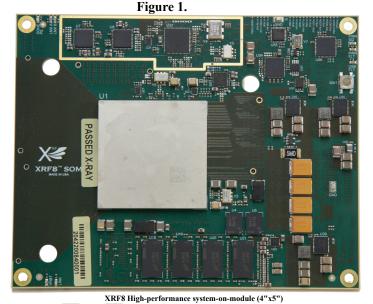

System-on-Module (SOM) with RF analog I/O, Ultrascale+ RFSoC FPGA, 8GB Memory, QuadMesh Interlink

#### **FEATURES**

- Eight 14-bit A/D inputs

- Eight 14-bit D/A outputs

- 700 mVp-p, direct-coupled, 50 ohm inputs

- 700 mVp-p, direct-coupled, 50 ohm outputs

- Xilinx Ultrascale+ ZU47/48 RFSoC/FPGA

- 2 Banks of 64-bit, 4GB DRAM (8 GB total)

- Ultra-low jitter programmable clock

- · External reference clock

- Multiboard, phase-aligned external trigger

- Four, independent mesh links each providing 20 Gbps sustained transfer rates

- 4.0" x 5.0" SOM module.

- · 40W typical power consumption

- · Conduction cooled via cold-plate

#### **APPLICATIONS**

- · Beam steering

- WLAN, WCDMA, WiMAX front end

- RADAR

- Medical Imaging

- High Speed Data Recording and Playback

- · IP development

#### SOFTWARE

- FrameWork Logic

- Petalinux Drivers

- C++ Host Tools

### DESCRIPTION

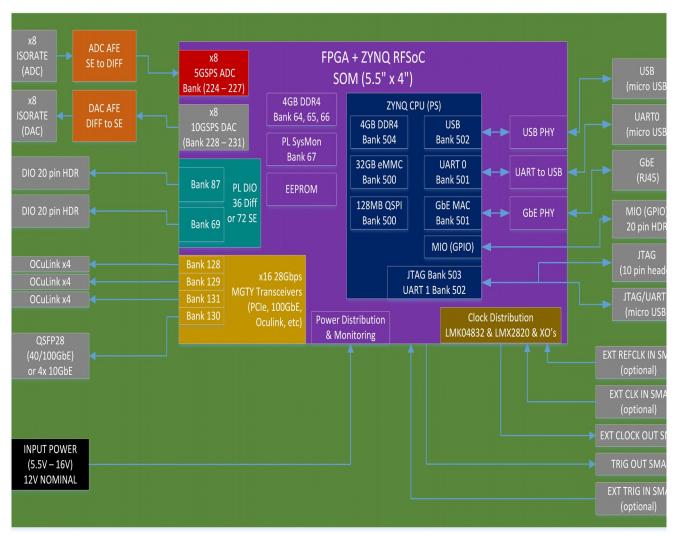

The XRF8 integrates eight (four IQ), digitizing channels and eight (four IQ) waveform generation channels with real-time signal processing on a SOM IO module for demanding, real-time DSP applications. The tight coupling of the analog I/O within the Ultrascale+ RFSoC FPGA core provides low latency, optimized for architectures such as beam-steering, SDR, RADAR, and LIDAR front end sensor digitizing and processing. The Quad Mesh system interface sustains transfer rates at 16 Gbps to four peers concurrently facilitating creation of large meshes within high performance real-time systems.

The onboard 1517-pin Xilinx ZU47/48DR with 8 GB external DDR4 RAM addressable as two 64-bit banks, provides a very high performance DSP core. On-chip integration of multichannel, GSPS analog IO, zero-wait SRAM block memory and quad ARM CPU cores enable real-time signal processing at extremely high rates.

The XRF8 exposes all eight of the RFSoC's (10.0 GSPS-capable) D/A channels and eight (5.0 GSPS-capable) A/D channels. On chip mixer and interpolator/decimator capabilities (respectively) can be enabled to implement concurrent, real-time frequency conversions. Sample clocks are generated via a cascaded ultra-low-jitter onboard PLL referenced either via an onboard, programmable 0.2-800 MHz TCXO or externally-supplied reference clock. Phase aligned, synchronous sampling of all channels at full hardware rates across multiple cards is possible if supplied and external reference clock and trigger operating in the reference clock domain.

The XRF8 can be fully customized using VHDL using the supplied board support package (BSP). The BSP provides standard IP cores for arbitrary waveform playback, and contiguous capture of ADC data of specified length (framed mode) DDR4 memory control and QuadMesh communications.

Software tools for target development include C++ libraries and drivers for Petalinux. Application examples demonstrating the module features and use are provided, including real-time, dynamic DAC waveform generation and analog captures.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Elk Solutions products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Elk Solutions standard warranty. Production processing does not necessarily include testing of all parameters.

RoHS

This electronics assembly can be damaged by ESD. Elk Solutions recommends that all electronic assemblies and components circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device to vary from published specifications.

### **ORDERING INFORMATION**

| Product                        | Part Number              | Description                                                                                                                                                                                                               |

|--------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XRF8                           | 2400007-<br><cfg>-</cfg> | SOM module with eight, 14-bit 5.0 GSPS A/D,<br>eight 10.0 GSPS 14-bit DAC, ZU47DR<br>Ultrascale+ RFSoC, 8GB DRAM.<br><cfg> is configuration:<br/>1 - Speed grade 1 FPGA</cfg>                                             |

| Single SOM<br>carrier/breakout | 24000011                 | Left: IsoRate8 x 2, DAC0-7, ADC0-7<br>Right: Ref, TrigIn, TrigOut, CLKOUT, SYNC,<br>Samtec 6-16V, Power SW,<br>1 GbE,<br>PL Oculink4 x 3, QSFP28,<br>Top: PL DIO,<br>Bottom: uUSB slave, uUSB JTAG, PS DIO, JTAG<br>6"x6" |

| Passive heatsink               | 008001113                | Thermal pad between RFSoC and heat spreader                                                                                                                                                                               |

| Active Fansink                 | 008001117                | Thermal pad between RFSoC and fansink assembly                                                                                                                                                                            |

| XRF8 FrameWork<br>Logic        | 55013                    | XRF8 board support package for VHDL.                                                                                                                                                                                      |

Figure 1: SOM Interface Block Diagram

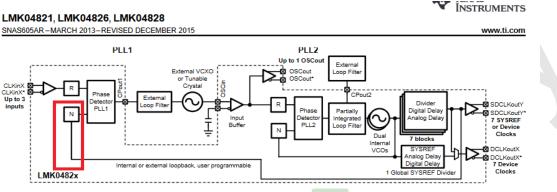

*Multiple-module synchronization:* In order to achieve synchronous operation among multiple boards, all must be provided phase-aligned references. The reference feeds an onboard LMK04832 PLL which operates in nested zero-delay mode to guarantee it's outputs are phase aligned with the reference input. If a simple tunable oscillator were used instead, nested zero-delay mode would not be available and multi-board synchronous operation would not be possible.

The LMK can accept an external reference clock operating at up to 750 MHz. If the reference rate exceeds the FPGA SYSREF clock rate (which is limited to < 10 MHz), a phase-aligned synchronization pulse must be presented to the LMK SYNC pin to phase align the LMK outputs of all boards in the system. This is essential to phase-aligned analog I/O across modules. Elk has exposed the LMK SYNC pin from the SOM for this very purpose. If the reference clock rate is less than 10 MHz, the LMK SYNC pin may be ignored.

A low-jitter, high-stability, external reference must be supplied to all modules operating at an integer submultiple the greatest common divisor of 16 and the chosen ADC and DAC sample rates. The onboard LMK PLL produces a lower-jitter SYSREF identical in rate and phase to EXT REF plus phase-aligned reference clocks for two LMX PLLs. The LMX PLLs can produce sample clocks covering the entire operational ranges of the ADC and DAC so they are used to synthesize the ADC and DAC sample clocks.

The diagram below is an excerpt from the LMK04832 datasheet.

Figure 19. Simplified Functional Block Diagram for Nested 0-delay Dual Loop Mode

The LMK employs a feedback loop to insure that the output frequency (SDCLKout/DCLKout) remains synchronous to the input reference clock (CLKin). An integer divider N (highlighted) is present in the feedback path, capable of dividing the output frequency by any integer (1-8192) to match the input frequency if needed to close the feedback loop.

The LMK is used on the XRF8 to generate the SYSREF signal used by the RFSoC as the timing references for the ADC and DAC subsystem. Xilinx imposes the following restrictions on SYSREF:

#### SYSREF Signal Requirements

The SYSREF signal is the timing reference for the system and must therefore be handled correctly to ensure it does not degrade the synchronization. This signal has the following requirements.

- 1. The SYSREF signal must be a high-quality, free-running, low-jitter square wave, to allow it to be captured consistently by the analog sample clock.

- 2. The SYSREF frequency must meet the following requirements:

- a. If synchronizing RF-ADC and RF-DAC tiles with different sample frequencies, the frequency must be an integer submultiple of:

- GCD(DAC\_Sample\_Rate/16, ADC\_Sample\_Rate/16)

- b. SYSREF must also be an integer submultiple of all PL clocks that sample it. This is to ensure the periodic SYSREF is always sampled synchronously.

- c. Less than 10 MHz.

In summary, the external reference supplied to the XRF8 must be a submultiple 16 and the chosen sample rates. If the external reference rate is greater than 10 MHz, a SYNC pulse must further be provided to all cards in the system to avoid phase indeterminacy.

*Triggering:* External trigger (EXT TRG) must operate in external reference (EXT REF) time domain. It must be marshaled into the external reference domain via a flip-flop that is clocked by SYSREF. This function can be performed by one of the XRF8 cards acting as master. ADC/DAC samples flow via the RFdc core in clumps (each 8, 16 or 32 samples (user-defined)), at an LMK-generated FSCLK rate of 200-400 MHz. Consequently, the synthesized multi-board synchronous trigger must reliably fall within a 1/FSCLK window on all cards, which is readily achievable.

### **Standard Features**

| nalog Inputs  |                                                         | Analog Output | 5                                                        |

|---------------|---------------------------------------------------------|---------------|----------------------------------------------------------|

| Channels      | 8                                                       | Channels      | 8 channels                                               |

| Range         | 700 mVp-p (typical)                                     | Range         | 700 mVp-p (typical)                                      |

| Туре          | Differential                                            | Туре          | Differential                                             |

| Coupling      | DC                                                      | Coupling      | DC                                                       |

| Impedance     | 50 ohm (typical)                                        | Impedance     | 50 ohm (typical)                                         |

| A/D Device    | RFSoC internal                                          | D/A Device    | RFSoC internal                                           |

| Resolution    | 14-bit                                                  | Resolution    | 14-bit                                                   |

| Sample Rate   | 100-5000 MSPS.                                          | Sample Rate   | 100-10000 MHz.                                           |

| mpedance      | 50 ohm +/- 1 ohm                                        | Impedance     | 50 ohm +/- 1 ohm                                         |

| Prog. Bias    | N/A                                                     | Prog. Bias    | N/A                                                      |

| FIFO size     | 128K for each active channel                            | FIFO size     | 128K for each active channel                             |

| Data transfer | RFdc driver                                             | Data transfer | RFdc driver                                              |

| Connectors    | Samtec SEAM8 30x8 female                                | Connectors    | Samtec SEAM8 30x8 female                                 |

| Clocking      | All ADCs synchronous. Integer relationship to DAC rate. | Clocking      | All DACs synchronous. Inter<br>relationship to ADC rate. |

Elk Solutions • phone 805.334.0314 • www.elkengineering.com

### **Standard Features**

| Analog Triggers           |                                                                      |

|---------------------------|----------------------------------------------------------------------|

| Number of<br>Triggers     | 1                                                                    |

| Source                    | SEAM40 connector, Software                                           |

| Functions                 | Start Trigger, Start Frame                                           |

| Source Level              | 1.6 Vdc                                                              |

| Modes                     | Edge, Level                                                          |

| Pulse width               | 6 min, 50 max (nS)                                                   |

| Accuracy                  | +/- 1 samples when trigger source and reference clock in same domain |

| Impedance                 | 50 +/- 1 ohm                                                         |

| Coupling                  | DC                                                                   |

| Protection<br>(power on)  | +/- 4V                                                               |

| Protection<br>(power off) | +/- 2V                                                               |

| Impedance                 | 50 ohm                                                               |

| Latency                   | Assert trigger on following SYSREF edge                              |

| Phase Locked Loop                     |                                                                                                                          |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Number of<br>PLLs                     | 3                                                                                                                        |

| Tuning<br>resolution/<br>restrictions | REF: See LMK04832 datasheet<br>ADC: See LMX2820 datasheet<br>DAC: See LMX2820 datasheet                                  |

| Reference<br>Frequency                | 1-750 MHz. 3.3V CMOS signal levels.                                                                                      |

| Reference<br>Source                   | SEAM40 HD connector pin or onboard osc                                                                                   |

| Clock Sources                         | Ext. or Int. TCXO                                                                                                        |

|                                       | External Inputs: 0 dBm nominal AC-<br>coupled, 50-ohm terminated, SMA                                                    |

| Jitter                                | Internal: <100 fs rms                                                                                                    |

| Channel<br>Clocking                   | All channels are synchronous                                                                                             |

| Multi-card<br>Synch                   | Must phase lock to external 1-750 MHz<br>system reference (SYSREF) using nest 0-<br>delay mode. 3.3V CMOS signal levels. |

Figure 2.

| RFSoC Digital processing configuration                    | Latency (Sample Clocks) | Latency ns(FS=6.4GSPS) | Latency ns (FS= 4GSPS) |

|-----------------------------------------------------------|-------------------------|------------------------|------------------------|

| DAC Datapath-all digitalfeature bypass (Min config)       | 160                     | 25                     |                        |

| DAC / 8x Interp, Inv-Sinc, NCO, QMC, ProgFilt(Max config) | 762                     | 119                    |                        |

| ADC Datapath-all digitalfeature bypass (Min config)       | 188                     |                        | 47                     |

| ADC / 8x Decim, NCO, QMC (Max config)                     | 412                     |                        | 103                    |

| ADC Analog front end & calibration                        | 95.54                   |                        | 23.89                  |

| NCO and QMC together                                      | 72                      | 11.25                  | 18                     |

| Decimation or Interpolation x8                            | 360                     | 56.25                  | 90                     |

| Decimation or Interpolation x4                            | 200                     | 31.25                  | 50                     |

| Decimation or Interpolation x2                            | 96                      | 15                     | 24                     |

| Decimation or Interpolation bypass                        | 16                      | 2.5                    | 4                      |

**RFSoC Latency operating at uniform 1 GSPS**

### **Standard Features**

| FPGA                               |                                                                                                                                                                                         |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device                             | Xilinx Ultrascale+ RFSoC<br>XCZU47-1FFVG1517E or I or XCZU48-<br>1FFVG1517E or I or XCZU58-<br>1FFVG1517E or I. See Xilinx document<br>DS889 v1.8, Table 9 for environmental<br>options |  |

| Speed Grade                        | -1 (extended temp)                                                                                                                                                                      |  |

| System Logic<br>Cells              | 930,000                                                                                                                                                                                 |  |

| CLB LUTs                           | 425,000                                                                                                                                                                                 |  |

| Maximum<br>Distributed<br>RAM (Mb) | 13                                                                                                                                                                                      |  |

| Block RAM<br>(Mb)                  | 38                                                                                                                                                                                      |  |

| UltraRam<br>(Mb)                   | 22.5                                                                                                                                                                                    |  |

| GTY<br>Transceivers                | 16 (all exposed to carrier)                                                                                                                                                             |  |

| Configuration                      | Two Micron<br>MT25QU512ABB8E12-0SIT TR QSPI<br>flash EEPROM. JTAG during development                                                                                                    |  |

| Memories                |                                                                                                                                                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM Size               | 8 GB total<br>8 devices @ 512Mb x16 each                                                                                                       |

| DRAM Type               | MT40A512M16LY-062E IT:E<br>DDR4 DRAM                                                                                                           |

| DRAM<br>Controller      | Controller for DRAM implemented in<br>logic. Each 64 bit interface uses 2.5 FPGA<br>I/O banks, 10@ 13 bit FPGA I/O Byte<br>lanes (4 per bank). |

| Total DRAM<br>Bandwidth | 38.4GB/s maximum bandwidth (100%<br>data bus efficiency, applications' efficiency<br>varies)                                                   |

#### Flash Disk

eMMC Size

Sandisk SDINBDG4-32G-XI1 device provides 32 GB of NV storage.

### **Standard Features**

| Monitoring |                                                                                                                                                                                                                 |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Alerts     | Firmware-specific. Typically,<br>Trigger Start, Trigger Stop, Queue<br>Underflow, Timestamp Rollover,<br>Temperature Warning and Failure.<br>32-bit counter with rollover and<br>resolution is 1 analog sample. |  |

| Digital IO       |                                                                                                                                                                                                                                                        |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of pins   | PL: 72, PS: 24                                                                                                                                                                                                                                         |  |

| Signal Standards | PL I/O: 24 differential I/O from bank<br>69 (48 s/e), plus 12 differential I/O<br>from bank 87 (24 s/e).<br>PS I/O: 14 s/e I/O from bank 502<br>(3.3V), and 10 s/e I/O from bank 501<br>(3.3V). There are no pins mapped to<br>SEAM8 from PS bank 500. |  |

| Connector        | Samtec SEAM8 connector                                                                                                                                                                                                                                 |  |

| Power               |                                                     |  |

|---------------------|-----------------------------------------------------|--|

| Consumption         | 5.5-16Vdc (40 Watts typical)                        |  |

| Temperature Monitor | Software with programmable alarms                   |  |

| Over-temp Monitor   | Disables power supplies                             |  |

| Power Control       | Channel enables and power up enables                |  |

| Heat Sinking        | Conduction cooling to chassis coldplate or heatsink |  |

| Physicals           |                              |  |

|---------------------|------------------------------|--|

| Form Factor         | Custom                       |  |

| Size                | 101x127mm                    |  |

| Weight              | 156g                         |  |

| Hazardous Materials | Lead-free and RoHS compliant |  |

| SoC I/O          |                                    |  |

|------------------|------------------------------------|--|

| Ethernet (1 GbE) | Signals upstream of phy on carrier |  |

| USB              | 1 root, 1 slave                    |  |

| MGT              | 8 x 25 Gbps (16 Gbps default)      |  |

| JTAG             | 14 pin JTAG (2mm pitch on carrier) |  |

| Connector        | Samtec SEAM8 connector             |  |

| Parameter                    | Тур        | Units   | Notes                                                                                                               |  |  |  |

|------------------------------|------------|---------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| A/D Performance – AC coupled | I          |         |                                                                                                                     |  |  |  |

| Analog Bandwidth             | 6000       | MHz     | -3dB.                                                                                                               |  |  |  |

| SFDR                         | 83<br>75   | dBc     | 71 MHz sine input, 95%FS, Fs = 4.0 GSPS<br>220 MHz sine input, 95%FS, Fs = 4.0 GSPS                                 |  |  |  |

| S/N                          | 56         | dBFS    | 170 MHz sine input, 98%FS, Fs = 1.0 GSPS                                                                            |  |  |  |

| SINAD                        | 57         | dBFS    | 170 MHz sine input, 95%FS, Fs = 1.0 GSPS                                                                            |  |  |  |

| ENOB                         | 9.3        | bits    | 170 MHz sine input, 98%FS, Fs = 1.0 GSPS                                                                            |  |  |  |

| Channel Crosstalk            | <80<br><80 | dB      | 71 MHz sine input, -3 dBm adjacent channel , Fs = 1.0 GSPS<br>71 MHz sine input, -3 dBm non-adjacent, Fs = 1.0 GSPS |  |  |  |

| Noise Density                | -132       | dBm/Hz  | Input grounded, Fs = 1.0 GSPS, 64K sample FFT, non-averaged                                                         |  |  |  |

| Gain Error                   | <1%        | % of FS | Calibrated                                                                                                          |  |  |  |

| Offset Error                 | <1         | mV      | Calibrated                                                                                                          |  |  |  |

| DAC Performance – AC Coupled | 1          |         |                                                                                                                     |  |  |  |

| Analog Bandwidth             | 6000       | MHz     | -3 dB                                                                                                               |  |  |  |

| SFDR                         | 78<br>70   | dBc     | 71 MHz @ -9 dBFS, 1000 MSPS sample rate<br>170 MHz @ -9 dBFS, 1000 MSPS sample rate                                 |  |  |  |

| IMD                          | -80<br>72  | dBc     | 71 MHz @ -9 dBFS, 1000 MSPS sample rate<br>170 MHz @ -9 dBFS, 1000 MSPS sample rate                                 |  |  |  |

| ENOB                         | 9.5        | bits    | 71 MHz sine output, AC coupled                                                                                      |  |  |  |

| Noise spectral density       | -145       | dBm/Hz  | 170 MHz @ 0dBFS, 1000 MHz sample rate                                                                               |  |  |  |

| Channel Crosstalk            | <65<br><70 | dB      | Aggressor = 71 MHz, -3 dBfs adjacent channel<br>Aggressor = 71 MHz, -3 dBfs non-adjacent channel                    |  |  |  |

| Gain Error                   | <1 %       | % of FS | Calibrated                                                                                                          |  |  |  |

| Offset Error                 | <500       | μV      | Calibrated                                                                                                          |  |  |  |

#### **Architecture and Features**

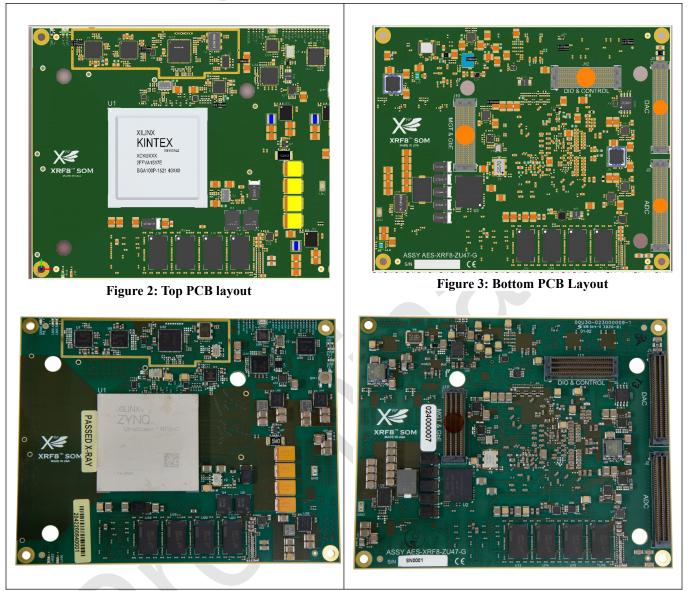

The XRF8 module architecture incorporates a Ultrascale MPSoC system-on-chip which incorporates quad ARM processors and dual real-time coprocessors, FPGA computing core, on chip RF analog I/O and Aurora QuadMesh core. These resources are integrated with external DDR4 external memories, ultra-low jitter programmable sample clock, boot flash and power management. The resulting architecture tightly couples the programmable FPGA fabric for real-time signal processing to the RF analog I/O with low latency and extremely high rates.

#### Analog IO

The RFSoC device provides eight A/D and D/A channels internally. All analog channels are exposed via connectors on the XRF8 SOM. Samtec IsoRate connectors are used to preserve the wide analog bandwidth for use in wideband and direct sampling applications.

The ADC and DAC devices are implemented directly on the FPGA die replacing gigabit transceiver tiles and are directly addressable by the logic fabric. In the standard logic provided in the BSP, the A/Ds have an interface component that receives the data, provides digital error correction (y=mx+b linearization), and a FIFO memory for buffering. The trigger manager within the firmware affords precise control over the collection of data. Trigger modes include frames of programmable size, continuous, external and software. Multiple cards can sample simultaneously by using external trigger inputs. The trigger component in the logic can be customized in the logic to accommodate new triggering requirements, should they arise. A non-volatile ROM on the card is used to store the calibration coefficients for the analog and is programmed during factory test.

#### FPGA Core

The XRF8 employs a Zynq Ultrascale+ RFSoC for DSP and control. This system-on-chip FPGA is capable of over 8.2 TeraMACs with over 4200 DSP elements. In addition to the raw processing power, the FPGA fabric integrates logic, memory and connectivity features that make the FPGA capable of applying this processing power to virtually any algorithm and sustaining performance in real-time. The FPGA has direct access to one 64-bit bank of (PL) DDR4 RAM. This memory allows the FPGA working space for computation, required by DSP functions like FFTs, and bulk data storage needed for system data buffering and algorithms like Doppler delay. An Axi DMA multiple-queue controller component is used to coordinate multiple data buffers in the DRAM that is used for system data buffering and algorithm support.

All IO, memory and host interfaces connect directly to the FPGA – providing direct connection to the data and control for maximum flexibility and performance. Firmware for the FPGA completely defines the data flow, signal processing, controls and host interfaces, allowing complete customization of the module functionality. Logic utilization of the standard Framework Logic is <15% of the device.

#### QuadMesh Host Interface

The XRF8 architecture delivers  $\sim 64$  Gbps sustained data rates over QuadMesh using the Aurora protocol. Packet systems can be implemented atop Aurora as an application interface layer to provide efficient, flexible inter-board transfers at high data rates. Typical packet data systems control the flow of packets using a credit system managed in cooperation with the mesh supervisor software.

The module has 16 high speed serial data links present on the HD connector. These are exposed via OcuLink connectors on the expansion carrier for system interconnect, operating at up to 16 Gbps per link, full duplex. These links enable modules to integrate into switched fabric systems to create powerful computing and signal processing architectures. The standard logic uses these lanes as four bonded Aurora ports of 4 lanes each. Other protocols such as sFPDP could be implemented in the FPGA.

#### **Digital IO**

72 digital lines are routed directly from the programmable logic (PL) fabric as length-matched differential pairs. These are useful for implementing low-latency state signaling, or interfacing to custom hardware devices via I2C, SPI or other common serial or parallel standards. An additional 24 lines are routed from the processor space (PS).

#### **Module Management**

The module has facilities for temperature monitoring within the FPGA die. The temperature sensor is monitored by a dedicated system monitor IP, so that power shuts when a critical temperature is exceeded. This function is independent of the FPGA but resident on-chip.

#### **FPGA Configuration**

The module uses a QSPI parallel FLASH memory to configure the Ultrascale+ RFSoC FPGA image. This FLASH can be programmed in-system using a supplied software applet.

During development, the JTAG interface to the FPGA may be used for development tools. The FPGA JTAG connector may be controlled using inexpensive USB Digilent debug aids providing compatibility with the Xilinx Platform USB Cable. However more commonly and conveniently, the target may boot PetaLinux and an ethernet connection used to facilitate insystem debugging via the Xilinx target communication framework (TCF).

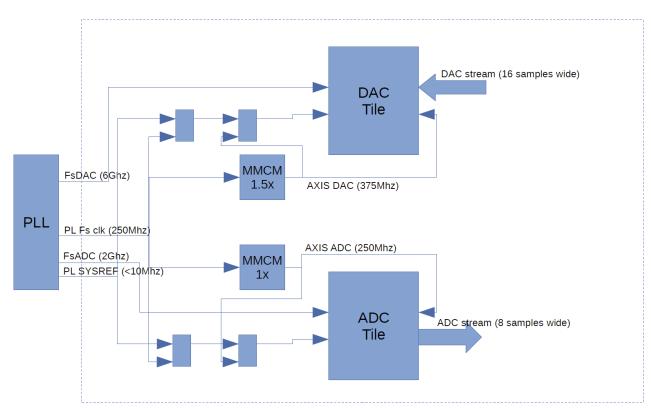

#### XRF8 clocking topology

The XRF8 supports heterogeneous ADC/DAC rates as shown in the figure below.

#### Figure 3.

Figure 4: Clocking topology

The XRF8 employs three PLLs to synthesize various clocks needed throughout the system. The first stage PLL is an LMK04832 which integrates two VCOs. Outputs from this PLL are used as follows:

| Output | Purpose                                                            |

|--------|--------------------------------------------------------------------|

| 0      | ADC_225_CLK (Reference to LMX A)                                   |

| 2      | ADC_224_CLK (Reference to LMX B)                                   |

| 7      | SYSREF_PL                                                          |

| 8      | LMX_2820 (Reference to LMX, which clocks DAC tiles 01)             |

| 10     | LMX_2820 (Reference to LMX, which clocks ADC tiles 01)             |

| 12     | FS_CLK (FPGA state machine clock which services ADC and DAC tiles) |

| 13     | SYSREF_IN                                                          |

Alternately, the XRF8 may be factory reconfigured to accept external reference and sample clocks may from its carrier if desired.

| Tcl Console   Messages   Log<br>Q                                                                                                                                                                                                                                                                                                                                                                                        | Reports Design Runs Power x DRC Methodology Timing                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Settings<br>Summary (16.086 W, Margin: N/A)<br>Power Supply<br>Utilization Details<br>Hierarchical (14.61 W)<br>Clocks (0.633 W)                                                                                                                                                                                                                                                                                         | Power analysis from implemented netlist. Activity derived from constraints                                                                                                                                                                                                                                                             | On-Chip Power                                                                                                                                    |

| <ul> <li>Signals (0.407 W)</li> <li>Data (0.378 W)</li> <li>Clock (nable (0.018 W)</li> <li>SetRieset (0.011 W)</li> <li>Legic (0.264 W)</li> <li>BRAM (0.564 W)</li> <li>URAM (0.223 W)</li> <li>FRAMS (5.317 W)</li> <li>Clock Manager (0.399 W)</li> <li>Clock Manager (0.399 W)</li> <li>GTY (3.84 W)</li> </ul> | Junction Temperature:         37.9°C           Thermal Margin:         62.7°C (79.2%)           Effective Bok         0.8°C/W           Power supplied to offship devices:         0 W           Confidence level:         Low           Laurch Proper Constrainer Advesser         6 Find and fix           inwahd switching activity | 91%<br>91%<br>0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                              |

| SYSMON (0.005 W)<br>PS (1.955 W)                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                        | Static:         1.477 W (5%)           9%         9%           9%         PL:         1.366 W (5%)           9%         PS:         0.111 W (7%) |

#### **Power Dissipation**

Power dissipation is heavily dependent on the firmware implementation. Typically, using more SERDES channels, more ARM cores and enabling RFdc core will increase power consumption.

The Xilinx power estimator for the supplied firmware design predicts baseline module power consumption to be approximately 16W and to increase modestly when either the the SERDES or RFdc cores are switched at full frequency.

| Import File         Export File         Quick Estimate         Manage IP         Snapshot         Set Default Rates         Reset to Default           Project         Confidence Level         Low - Early Estimatio         Last Updated: 6:26:2019           Settings         Summary         Last Updated: 6:26:2019         Last Updated: 6:26:2019           Settings         Summary         Statumary         Statumary         Statumary         Statumary           Project         Confidence Level         Low - Early Estimatio         Last Updated: 6:26:2019           Settings         Summary         Statumary         Statumary         Statumary           Project         Confidence Level         Numerial Margin         58: 0: 0: 1W         9%         Statumary         0000           Statuc         2: 0: CW         Conce         Power         Statuc         0: 0: 0: 0: 0: 0: 0: 0: 0: 0: 0: 0: 0: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                      |           | illinx Power Estimator (XPE) - 2019.1<br>aScale+™, Virtex® UltraScale+, Zynq® U |                       |               | Ditrascale+ Release: 29-May-1 |                       |                   |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|-----------|---------------------------------------------------------------------------------|-----------------------|---------------|-------------------------------|-----------------------|-------------------|----------|

| Settings         Device         Settings         Device         Settings           anily         Zyng UttraScale+ RFSoC         Zyng UttraScale+ RFSoC         Settings         Setings         Setings         Setings </th <th></th> <th></th> <th></th> <th>te Mana</th> <th colspan="2">Manage IP</th> <th></th> <th></th> <th colspan="2">Reset to Defaults</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                      |           | te Mana                                                                         | Manage IP             |               |                               |                       | Reset to Defaults |          |

| Device         Openation         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Project           |                      | C         | Confidence L                                                                    | əvel <sub>Low-E</sub> | arly Estimati | on                            | Last                  | Updated: 6/2      | 6/2019   |

| Imitig         Zyng UltraScale+ RFSoC           wick         https://dx.ustical           wick         https://dx.ustical           beed Grade         2           app Grade         iduatitial           ocess         Typical           bringer Diracd         iduatitial           ocess         Typical           bringer Diracd         iduatitial           ocess         Typical           bringer Diracd         reduction (= 19% accurrery)           Environment         ReAM           network         169 Power           Brand Harger         250 UFM           Brand Harger         250 UFM           Brand Harger         250 UFM           Brand Harger         167 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Settings          |                      |           | -                                                                               |                       | Sı            | ımma                          | ry                    |                   |          |

| Imply         Zyng Utrascale + FS sc         Common Scheme         Schem         Schem         Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | Device               |           | Total On-                                                                       | Chin Power            | 39.5          | w                             | 0% •                  | Transceiver       | 0.0000   |

| ackage       FSVF1760       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       10000       1000       1000 <td>amily</td> <td>Zynq UltraScale+</td> <td>RFSoC</td> <td></td> <td></td> <td></td> <td></td> <td>5% •</td> <td>MO</td> <td>1.809</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | amily             | Zynq UltraScale+     | RFSoC     |                                                                                 |                       |               |                               | 5% •                  | MO                | 1.809    |

| beed Grade       2       0.7 cm       Nor registed to decide to the de                 | evice             | XCZU39DR             |           |                                                                                 |                       | 54.2 *        | с                             | 91% •                 | PS+FPGA Dyn.      | 35.897   |

| Imp Grado         Imp Grado <thimp grado<="" th=""> <thimp grado<="" th=""> <thi< td=""><td></td><td>FSVF1760</td><td></td><td></td><td></td><td>45.8°C</td><td>59.1W</td><td>5% •</td><td>Device Static</td><td>1.800W</td></thi<></thimp></thimp>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | FSVF1760             |           |                                                                                 |                       | 45.8°C        | 59.1W                         | 5% •                  | Device Static     | 1.800W   |

| Ordensis     Typical       Transacterization     Froduction (s 15% accuracy)       Residential formation (s 15% accuracy)       Resideni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | -2                   |           | Effective 6                                                                     | JA                    | 0             | .7 °C/W                       | Power supplied to of  | f-chip devices    | 0.2300   |

| Resource         Power<br>(ump to absect (V/O)         Power<br>(V)         Power<br>(V)         Source         Votage         Total (f           Environment<br>nbient Temperature         Environment<br>(User Override         Environment<br>(User Overide         Environment<br>(User Override <td< td=""><td></td><td>Industrial</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                             |                   | Industrial           |           |                                                                                 |                       |               |                               |                       |                   |          |

| haracterization       Production (s 15% accuracy)         Environment       Curre to bateff         Inclini Temperature       User Override         25.0 °C       Curre to bateff         Organic       Pill         Oparatic       Pill         Disad       Sink         Heid De Override       25.0 °C         Carl Solid       Disad         Disad       Sink         Messages       22.3 °C/H         No       1.00 0.00 0         Transceived       GTV         PL       0.117 0         U/O       1.006 0         Transceived       GTV         PS       0.684 2         Static       0.100 0         PL Implementation       Power Optimization         PL Static       0.146 do         Most VAC:       1.066 do         Most VAC:       0.00 0.00 0         PL Static       0.146 do         Most VAC:       1.066 do         Most VAC:       1.060 0.00 0         Most VAC:       1.000 0.00 0         PS Power Raits       1.000 0.00 0         PS Power Raits       1.000 0.00 0         PS Power Raits       1.000 0.00 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   | Typical              |           |                                                                                 |                       |               |                               | Power                 |                   |          |

| Million         Core         2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 4 - 7 + 1 - 2 - 2 - 5 + 1 - 1 - 2 - 1 - 5 + 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                      |           | Res                                                                             |                       |               |                               | Source                | Voltage           | Total (A |

| Environment         LOGIC         9.39         25           Inction Temperature         User Override         25.0 °C         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | haracterization   | Production (± 15%    | accuracy) |                                                                                 | (Jump to sheet)       | (VV)          | (%)                           | VCCINT                | 0.850             | 21.80    |

| BRAMI         1057         Image: Constraint of the sector |                   |                      |           |                                                                                 | CLOCK                 | 2.584         | 7                             | V <sub>CCINT_IO</sub> | 0.850             | 0.57     |

| httert Temp         25 0 °C           Core         DSP         4 250 11           Mow         25 0 °C           PL         0.22 °C           Dynamic         PLL         0.22 °C           Other         16 733 42           High Profile         23 °C/V           SAM Selection         Small (4*x4*)           ard Selection         Small (4*x4*)           VO         100           DB 3avard Temperature         100           DB 3avard Temperature         12 to 15           DB 3avard Temperature         1556 dt           Messages         1656 dt           Messages         1800           Messages         1800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                      |           |                                                                                 | LOGIC                 | 9.939         | 25                            | VCCBRAM               | 0.850             | 0.16     |

| Core         PLL         0.227         1           Mow         250 LFM         1         0.00         0.27         1           Mow         250 LFM         1         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00         0.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | User Override        |           |                                                                                 | BRAM                  | 1.057         | 3                             | VCCAUX                | 1.800             | 0.56     |

| Piccore         Piccore <t< td=""><td></td><td></td><td>25.0 °C</td><td>Core</td><td></td><td>4.250</td><td>11</td><td>Vccaux_io</td><td>1.800</td><td>0.43</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                      | 25.0 °C   | Core                                                                            |                       | 4.250         | 11                            | Vccaux_io             | 1.800             | 0.43     |

| Bits         Differ         Differ <thdiffer< th=""> <thdifer< th=""> <thdiffer< th=""></thdiffer<></thdifer<></thdiffer<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   | User Override        |           |                                                                                 |                       | 0.227         | 1                             | V <sub>cco</sub> 3.3V | 3.300             |          |

| B3A         97 - 500         92.3 (CV)         Hard P         0.117         0         V20.0 15V         15.00           Varial Selection         Small (4'x4')         U         U         0.01         0.00         V20.0 15V         15.00           Varial Selection         Small (4'x4')         U         0.01         0.000         V20.0 13V         1.350         V20.0 13V         1.350         V20.0 13V         1.350         V20.0 13V         1.350         V20.0 14V         V20.0 14V         1.500         V20.0 14V         V20.0 14V         1.500         V20.0 14V         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |                      | 250 LFM   |                                                                                 |                       |               | 1                             | V <sub>cco</sub> 2.5V | 2.500             |          |

| PL         Implementation<br>Power Optimization         Implementation<br>PL Static         Implementatic                                                                                                                                                                                                                                                                                        |                   | High Profile         |           |                                                                                 | Other                 | 16.735        | 42                            | V <sub>cco</sub> 1.8V | 1.800             | 0.21     |

| ± of Board Layers       12 to 15         UO       100       1809 is         D/B       Transceiver       0         D/B and Temperature       0       0         PL Implementation       PS Oynamic PS       0.684 2         Nessages       1.656 4       0         Messages       0       0.000 0         INX Power Advantage (check for updates)       Ele Support Request (WebCase)       Xlinx Power Advantage Check for updates)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                      | 92.3 °C/W |                                                                                 | Hard IP               | 0.117         | 0                             | Vcco 1.5V             | 1.500             |          |

| DBB     Transceiver     GTV     0.000       Baard Temperature     GTV     0.000     RFADC-DAC Power Rais       PL Implementation     PS     0.684     2       Messages     0.144     0     RFADC-DAC Power Rais       Messages     1.656     MGTV-Xvrr     1.800       MSP over Advantage (check for updates)     Ele Support Request (WebCase)     Mins Power Estimator User Cond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                      |           |                                                                                 |                       |               |                               |                       |                   |          |

| Board Temperature     Transceiver     GTY     0.000       PL Implementation     PS Dynamic     PS     0.684     2       Age/Optimization     Power Optimization     PL Static     0.144     0       Messages     MGTYAV:r     1.800     MGTYAV:r     1.800       Missing Check for updates)     Ele Support Request (WebCase)     Xlinx Power Estimator User Can                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 12 to 1              | 5         | /C                                                                              | 10                    | 1.809         | 5                             | V <sub>cco</sub> 1.2V | 1.200             | 0.44     |